Ein Beispiel-Programm bzw. Beispiel-Initialsierung für USCI (Universial Serial Communication Interface) mit dem MSP430G2553 (im SPI-Mode). Das Programm an sich ist fast identisch mit dem Programm aus “MSP430 USI Initialisierung“. Es werden also wieder Bytes (0-255) an das Schieberegister gesendet.

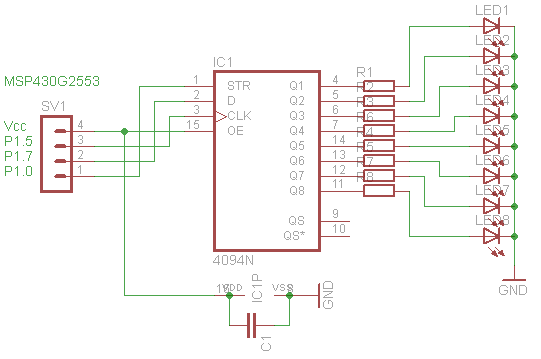

Schaltplan

C-Programm

/*************************************************

* ___ _ _

* | |_ _ _| |___ ___ _| |___

* | | |_'_| . | -_| _|_| . | -_|

* |___|_,_|___|___|___|_|___|___|

*

* FILE: main.c

* Author: declis (xdec.de)

************************************************/

#include <msp430g2553.h>

#define strobe BIT0 // strobe @ P1.0

#define data BIT7 // data out @ P1.7

#define clock BIT5 // CLK out @ P1.5

#define ms 100

void main(void)

{

unsigned char m_sec=ms;

WDTCTL=WDTPW+WDTHOLD; // stop WDT

BCSCTL1=CALBC1_1MHZ; // SMCLK=~1MHz

DCOCTL=CALDCO_1MHZ;

P1DIR|=strobe;

P1OUT&=~strobe;

// USCI_B0 clock output, USCI_B0 SPI Mode: master out

P1SEL|=clock+data;

P1SEL2|=clock+data;

// USCI in reset state

UCB0CTL1|=UCSWRST;

// SPI Master, 8bit data length, LSB first, synchronous mode

// data captured on first UCLK edge, changed on the following edge

UCB0CTL0|=UCMST+UCSYNC+UCCKPH;

// USCI CLK-SRC=SMCLK=~1MHz

UCB0CTL1|=UCSSEL_2;

// USCI released for operation

UCB0CTL1&=~UCSWRST;

// enable TX interrupt

IE2|=UCB0TXIE;

// clear TXIFG

IFG2&=~UCB0TXIFG;

_EINT(); // enable interrupts

while(1)

{

while(IFG2&UCB0TXIFG); // TX buffer ready?

UCB0TXBUF++; // increment TX buffer (0-255)

while(m_sec--) // wait some time (100ms)

__delay_cycles(1000);

m_sec=ms;

}

}

#pragma INTERRUPT (USCI)

#pragma vector=USCIAB0TX_VECTOR

void USCI(void)

{

// transmission done

P1OUT|=strobe; // enable strobe register

P1OUT&=~strobe;

IFG2&=~UCB0TXIFG; // clear TXIFG

}